Código QR

Sobre nós

Produtos

Contate-nos

Telefone

Fax

+86-579-87223657

E-mail

Endereço

Wangda Road, Ziyang Street, condado de Wuyi, cidade de Jinhua, província de Zhejiang, China

O polimento químico-mecânico (CMP) remove o excesso de material e defeitos superficiais através da ação combinada de reações químicas e abrasão mecânica. É um processo chave para alcançar a planarização global da superfície do wafer e é indispensável para interconexões de cobre multicamadas e estruturas dielétricas de baixo k. Na fabricação prática, o CMP não é um processo de remoção perfeitamente uniforme; dá origem a defeitos típicos dependentes de padrão, entre os quais a inclinação e a erosão são os mais proeminentes. Esses defeitos afetam diretamente a geometria das camadas interligadas e suas características elétricas.

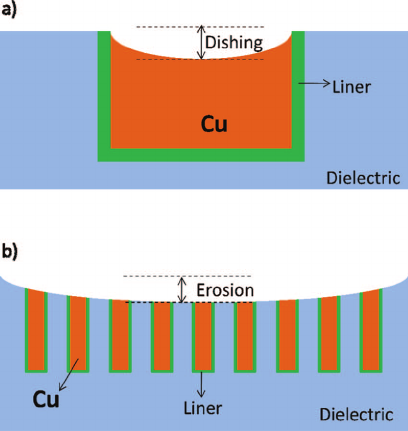

Dishing refere-se à remoção excessiva de materiais condutores relativamente macios (como o cobre) durante o CMP, levando a um perfil côncavo em forma de prato dentro de uma única linha de metal ou de uma grande área metálica. Na seção transversal, o centro da linha metálica fica abaixo de suas duas bordas e da superfície dielétrica circundante. Este fenômeno é freqüentemente observado em linhas largas, almofadas ou regiões metálicas do tipo bloco. Seu mecanismo de formação está relacionado principalmente às diferenças na dureza do material e à deformação da almofada de polimento em características metálicas amplas: metais macios são mais sensíveis aos componentes químicos e abrasivos na pasta, e a pressão de contato local da almofada aumenta em características largas, fazendo com que a taxa de remoção no centro do metal exceda aquela nas bordas. Como resultado, a profundidade do côncavo geralmente aumenta com a largura da linha e o tempo de polimento excessivo.

A erosão é caracterizada pela altura geral da superfície em regiões de alta densidade de padrões (como matrizes de linhas de metal densas ou áreas com preenchimento simulado denso) sendo menor do que nas regiões esparsas circundantes após o CMP. Em essência, é uma remoção excessiva de material em nível de região, orientada pela densidade do padrão. Em regiões densas, o metal e o dielétrico juntos proporcionam uma área de contato efetiva maior, e o atrito mecânico e a ação química da almofada e da pasta são mais fortes. Consequentemente, as taxas médias de remoção de metal e dielétrico são mais altas do que em regiões de baixa densidade. À medida que o polimento e o polimento excessivo prosseguem, a pilha metal-dielétrica em áreas densas torna-se mais fina como um todo, formando um degrau de altura mensurável, e o grau de erosão aumenta com a densidade do padrão local e a carga do processo.

Do ponto de vista do desempenho do dispositivo e do processo, a inclinação e a erosão têm múltiplos impactos adversos nos produtos semicondutores. O prato reduz a área transversal efetiva do metal, levando a uma maior resistência de interconexão e queda de IR, o que por sua vez causa atraso no sinal e redução da margem de temporização em caminhos críticos. Variações na espessura dielétrica causadas pela erosão alteram a capacitância parasita entre as linhas metálicas e a distribuição do atraso RC, prejudicando a uniformidade das características elétricas no chip. Além disso, o afinamento dielétrico local e a concentração do campo elétrico afetam o comportamento de ruptura e a confiabilidade a longo prazo dos dielétricos intermetálicos. No nível de integração, a topografia superficial excessiva aumenta a dificuldade de foco e alinhamento da litografia, degrada a uniformidade da subsequente deposição e gravação do filme e pode induzir defeitos como resíduos metálicos. Em última análise, esses problemas se manifestam como flutuação de rendimento e uma janela de processo cada vez menor. Portanto, na engenharia prática, é necessário controlar a inclinação e a erosão dentro de limites especificados através da equalização da densidade do layout, otimização depolimento mpressaseletividade e ajuste fino dos parâmetros do processo CMP, de modo a garantir a planaridade das estruturas de interconexão, desempenho elétrico estável e fabricação robusta de alto volume.

+86-579-87223657

Wangda Road, Ziyang Street, condado de Wuyi, cidade de Jinhua, província de Zhejiang, China

Copyright © 2024 VeTek Semiconductor Technology Co., Ltd. Todos os direitos reservados.

Links | Sitemap | RSS | XML | política de Privacidade |